概述

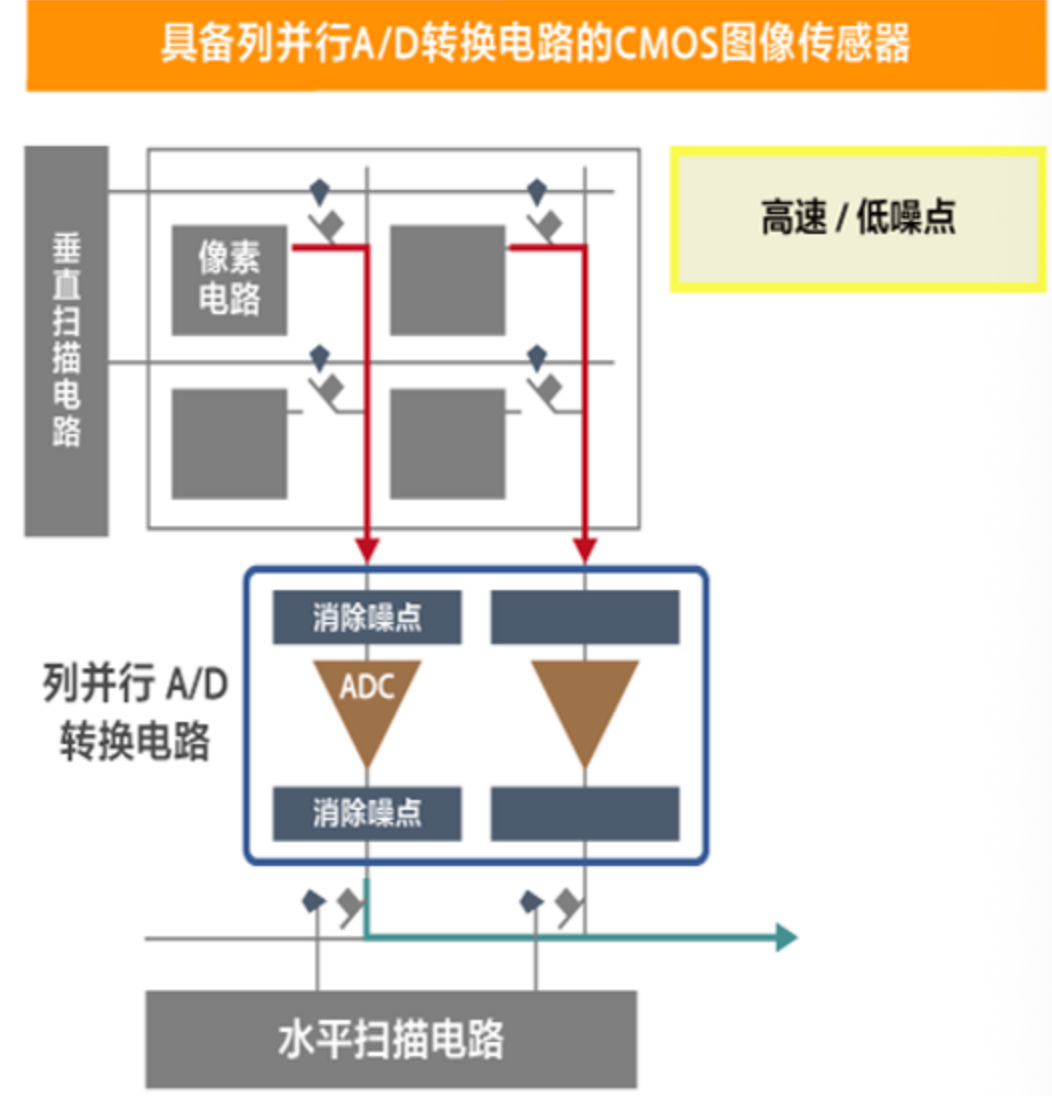

图像传感器作为数字成像系统的核心前端器件,其性能直接决定成像质量与系统响应速度。随着高分辨率、高帧率成像需求的不断提升(如4K/8K视频、高速机器视觉、自动驾驶等场景),传统单通道A/D转换架构因数据吞吐量不足、传输噪声叠加等问题,已难以满足应用需求。列并行A/D转换电路通过为像素阵列的每一列配置独立或共享的A/D转换单元,实现模拟信号的并行量化,有效突破了单通道架构的速度瓶颈,同时缩短了模拟信号传输路径,降低了噪声干扰,成为高性能CMOS图像传感器的核心解决方案之一。本文将从架构选型、核心技术设计、典型实现方案、性能优化策略及应用前景等方面,全面阐述图像传感器芯片列并行A/D转换电路的解决方案。

在图像传感器的A/D转换架构中,主要存在单通道、列并行和像素并行三种主流方案。单通道架构因所有像素共享一个A/D转换器,虽具备高填充因子和良好成像质量,但转换速度受限,无法适配高帧率需求;像素并行架构为每个像素配备独立A/D单元,转换速度最快,但存在填充因子低、功耗与面积成本过高的固有缺陷。列并行架构则平衡了速度、功耗与面积的需求,其核心优势在于:一是并行处理提升帧率,每列共享的A/D单元可同步处理列内像素信号,大幅提升数据吞吐量;二是缩短传输路径降噪,模拟信号在列内完成量化,避免了长距离传输导致的噪声叠加与信号衰减;三是工艺兼容性强,可与CMOS工艺深度集成,便于实现系统级芯片(SoC)设计。

根据核心转换单元的类型,列并行A/D转换架构可分为以下三类:

列并行单斜率ADC(SS-ADC)架构:

采用“斜坡发生器+比较器+计数器”的极简结构,所有列共享一个斜坡发生器,每列配置独立比较器与计数器。工作时,斜坡发生器输出单调变化的参考电压,与列内像素的模拟信号进行比较,当两者相等时锁存计数器数值,完成量化。该架构具有结构简单、面积紧凑、功耗低的特点,是目前主流的列并行方案,广泛应用于手机、安防等消费级与工业级图像传感器。

列并行循环ADC(Cyclic-ADC)架构:通过多次迭代逼近实现高精度量化,核心单元包括比较器、乘法数模转换器(MDAC)和移位寄存器。每列配置一套循环转换单元,通过重复“比较-放大-反馈”流程提升分辨率。该架构在保证中等速度的前提下,可实现12位以上高精度转换,适用于对成像质量要求较高的医疗成像、专业摄影等场景。

列并行1位比较器迭代架构:每列配置1位简单比较器,通过在像素信号积分过程中分阶段完成位量化(如每阶段确定2位,4阶段完成8位量化)。该方案大幅简化了比较器设计,降低了面积与功耗,适合低功耗、高集成度的智能图像传感器。

列并行A/D转换电路的性能核心取决于三个关键指标:分辨率(动态范围)、转换速度(帧率)和功耗,其设计难点在于如何在有限的列间距内,实现低噪声、高精度、低功耗的并行量化。以下是核心模块的设计要点:

比较器是列并行A/D转换的核心单元,其噪声水平直接决定转换精度。列并行架构中,比较器需在紧凑的面积内实现低噪声性能,主要采用以下设计策略:一是采用高增益单端比较器,通过优化晶体管尺寸与偏置电流,降低热噪声与闪烁噪声,在3.24μm像素尺寸下可实现2.4e⁻rms的低噪声水平;二是引入动态偏置技术,通过开关电容控制偏置电流,在转换阶段提供高增益以保证精度,空闲阶段降低偏置电流以节省功耗,如开关电容控制的低功耗动态偏置比较器,可使列平均功耗降至63.2μW;三是采用双噪声消除技术,对模拟电路的复位噪声与数字电路的耦合噪声进行高精度抵消,进一步提升信号纯净度。

参考信号的稳定性直接影响量化精度,尤其是列并行架构中多列共享参考源时,需保证信号的一致性与温度稳定性。设计要点包括:一是采用带隙基准电压电路,生成不受温度变化影响的参考电压,可提供四组高精度基准电压供多列ADC共享;二是优化斜坡发生器设计,对于SS-ADC架构,采用电流源驱动的电容充放电电路,通过校准技术补偿电容漂移与电流偏差,实现线性度优良的斜坡信号;三是引入增益自适应结构,基于开关电容调整量化步长,补偿光子散粒噪声的影响,提升动态范围,经校准后可实现13位动态范围。

列并行架构需保证所有列的A/D转换单元同步工作,同时实现高效的数据读出,避免数据冲突。关键设计包括:一是采用全局时钟同步机制,通过时钟发生器生成高精度时序信号,控制斜坡发生器、比较器与计数器的同步工作,确保多列量化的一致性;二是设计低翻转次数的双向双边沿计数器,减少数字电路的开关噪声,同时提升计数效率;三是采用多工器(MUX)实现并行数据的串行输出,例如将8个列ADC分为一组,通过8位MUX汇总后从单个引脚输出,平衡并行处理与引脚数量的矛盾。

随着像素尺寸不断缩小(如1.12μm),列间距愈发紧凑,传统平面集成难以满足电路面积需求。堆叠工艺成为列并行ADC集成的关键技术:一是采用双芯片堆叠架构,将传感器像素(采用定制传感器工艺)与列ADC逻辑电路(采用先进CMOS逻辑工艺)分别集成在上下芯片,通过硅通孔(TSV)实现列信号的高效传输,该架构可使列ADC面积缩小至2.24×365μm²;二是引入三层堆叠架构,在传感器层与逻辑层之间增加DRAM缓存层,实现高帧率数据的临时存储,可在全高清分辨率下实现960fps的超慢动作录制;三是采用芯片级晶圆键合(CoW)技术,对于大光学格式传感器,将多个逻辑芯片堆叠在传感器芯片上,通过微凸块实现高密度连接,提升面积效率。

基于上述核心技术,业界已提出多种成熟的列并行A/D转换解决方案,覆盖从消费级到专业级的不同应用场景,以下是两类典型方案:

低功耗列并行增益自适应SS-ADC方案

该方案针对高分辨率消费级图像传感器设计,采用TSMC 180nm工艺实现,核心特点是通过增益自适应技术提升动态范围,同时优化电路结构降低功耗。关键设计包括:一是采用SS-ADC架构,每列配置独立比较器与计数器,共享斜坡发生器;二是引入开关电容式增益自适应结构,根据像素信号强度调整量化步长,补偿低光环境下的噪声影响;三是采用动态偏置比较器与低翻转计数器,降低静态与动态功耗。实测性能指标:列平均功耗63.2μW,动态范围13位(校准后),随机噪声1.2e⁻,FoM₁值1.08e⁻·nJ/pixel,FoM₂值0.29e⁻·pJ/step。基于该方案实现的500万像素CMOS图像传感器,采用SEC 90nm BSI工艺,系统总功耗135.8mW,满足智能手机、平板电脑等移动设备的低功耗需求。

高精度列并行循环ADC方案

该方案面向高速、高精度工业视觉与医疗成像场景,采用TSMC 0.18μm CMOS RF混合信号工艺实现,核心是通过循环迭代架构提升分辨率。关键设计包括:一是每列配置一套12位循环ADC单元,包含高增益比较器与MDAC模块;二是集成列并行相关双采样(CDS)电路,消除像素复位噪声;三是采用全局同步时序控制,保证64×64像素阵列的并行转换同步性。实测性能指标:ENOB大于11位,单列ADC面积11254μm²,CDS电路面积2042μm²,全芯片功耗小于90mW,64×64像素阵列循序扫描帧率达520fps,可满足HD TV 1080p规格的高帧率需求。

列并行A/D转换电路的设计本质是噪声、功耗与面积的三者权衡,针对不同应用场景的需求,可采用以下优化策略:

噪声优化策略:对于低光照成像场景,采用数字相关双采样(D-CDS)技术消除复位噪声与固定模式噪声;引入多ADC冗余设计,将单个像素信号分配给两个ADC并行转换,通过数据平均降低随机噪声;优化比较器输入级晶体管尺寸,提升增益并降低闪烁噪声。

功耗优化策略:采用动态电源管理技术,在帧间隙关闭闲置列的ADC单元;优化时序设计,减少数字电路的翻转次数;采用低电压工艺(如65nm、40nm),在保证性能的前提下降低电源电压与功耗。

面积优化策略:简化ADC核心单元结构,如采用1位比较器迭代架构替代高精度比较器;采用堆叠工艺将ADC逻辑电路与传感器像素分层集成,充分利用垂直空间;复用列内电路模块,如多列共享参考源与时钟驱动电路。

列并行A/D转换电路作为高性能CMOS图像传感器的核心技术,已广泛应用于智能手机、安防监控、工业视觉、自动驾驶、医疗成像等领域。随着应用需求的升级,未来将呈现以下发展趋势:

更高分辨率与帧率:通过先进工艺(如3nm、2nm)与堆叠架构优化,实现16位以上分辨率与1000fps以上帧率,满足超高清视频与高速运动捕捉需求。

低功耗与高集成度:结合近阈值计算、异步电路设计等技术,进一步降低功耗;将AI加速器与列并行ADC集成,实现“感知-量化-计算”一体化,提升智能图像传感器的性能。

多维度传感融合:在列并行架构基础上,集成红外、深度等多模态传感的A/D转换单元,实现多维度图像数据的并行采集与融合处理。

极端环境适应性:针对汽车、航天等极端环境,优化电路的温度稳定性与抗辐射性能,提升列并行ADC的可靠性与鲁棒性。

列并行A/D转换电路通过并行量化架构,有效平衡了图像传感器的分辨率、帧率、功耗与面积需求,是高性能CMOS图像传感器的核心解决方案。其设计核心在于通过低噪声比较器、高精度参考信号、同步时序控制与堆叠集成技术,实现多列信号的高效、精准量化。不同应用场景需根据性能需求选择合适的架构(如SS-ADC适用于低功耗场景,循环ADC适用于高精度场景),并通过噪声、功耗与面积的权衡优化,获得最优设计方案。未来,随着工艺进步与架构创新,列并行A/D转换电路将向更高性能、更高集成度、多维度融合的方向发展,为各类智能成像应用提供更强的技术支撑。

技术优势与创新点 高效转换策略:分段逐次逼近结合动态区段选择,较传统SAR减少30%以上转换周期,提升能效比。过采样+数字校正技术实现14bit等效精度,满足医疗影像、工业检测等严苛场景需求。通过运放共享、RSD算法与紧凑DAC设计,单ADC面积缩小40%,适配超薄摄像头模组。全差分结构与多层屏蔽设计,PSRR提升至70dB,适应车载电子等电磁干扰环境。支持动态分辨率切换(如强光下10bit高速模式,暗光下14bit低噪模式),平衡性能与功耗。架构兼容10–16bit分辨率,适配BSI、Stacked等多种先进工艺,具备长期技术生命力。采用分段逐次逼近与动态区段选择相结合的算法,相较传统逐次逼近寄存器(SAR)减少了30%以上的转换周期,显著提升了能效比。动态区段选择通过实时监测输入信号幅度,自动调整转换区间,从而提高转换速度。

运用过采样技术与数字校正算法,实现14bit等效精度,满足医疗影像与工业检测等对精度要求极高的应用场景。过采样技术通过增加采样频率来提升信噪比,而数字校正技术则有效补偿了电路非线性误差。借助运放共享、RSD算法和紧凑型DAC设计,将单ADC的面积缩小了40%,更适应于超薄摄像头模组。运放共享通过复用模拟电路中的运算放大器,大幅减少了芯片面积。采用全差分信号处理结构与多层屏蔽设计,将电源抑制比(PSRR)提升至70dB,使其具备出色的抗干扰性能,能够在车载电子等强电磁环境中稳定工作。